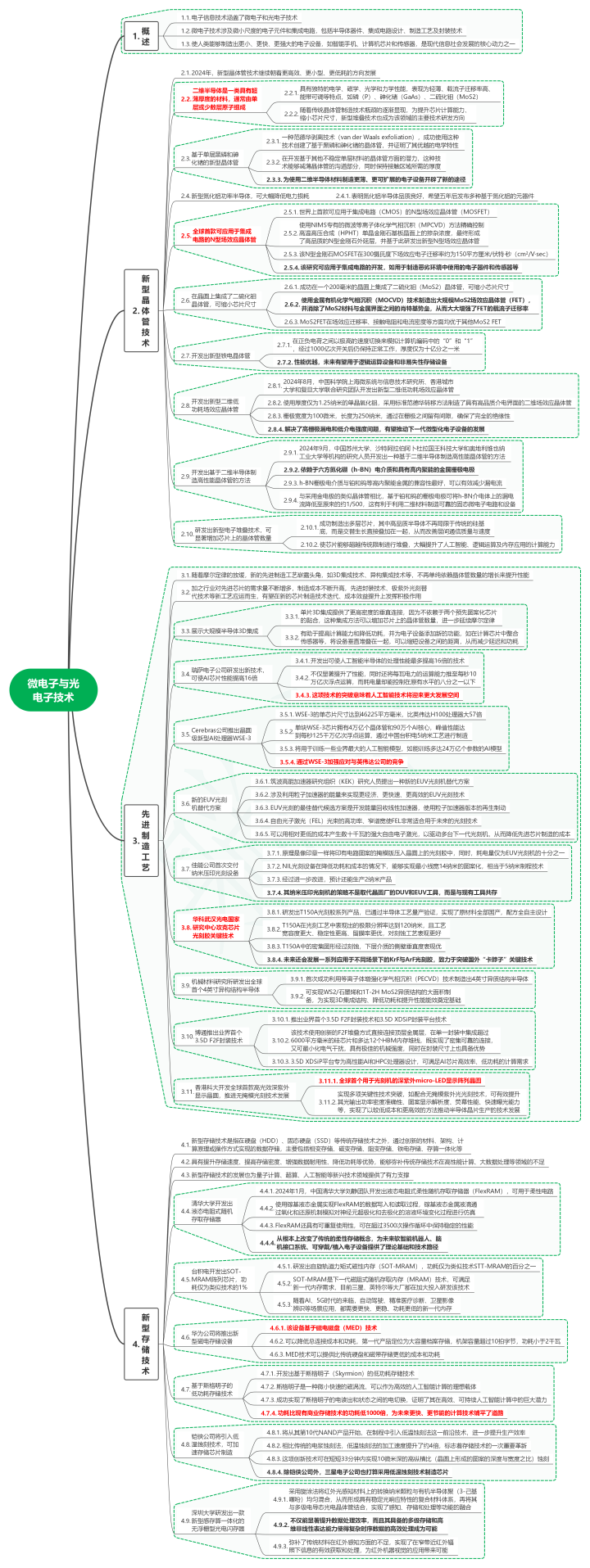

1. 轮廓

1.1. 电子信息本事涵盖了微电子和光电子本事

1.2. 微电子本事触及轻细门径的电子元件和集成电路,包括半导体器件、集成电路联想、制造工艺及封装本事

1.3. 使东说念主类八成制造出更小、更快、更坚硬的电子成立,如智高东说念主机、缱绻机芯片和传感器,是当代信息社会发展的中枢能源之一

2. 新式晶体管本事

2.1. 2024年,新式晶体管本事持续朝着更高效、更微型、更低耗的主张发展

2.2. 二维半导体是一类具有超薄厚度的材料,时常由单层或少数层原子构成

2.2.1. 具有独到的电学、磁学、光学和力学性能,阐发为浮滑、载流子移动率高、能带可调等特色,如磷(P)、砷化锗(GaAs)、二硫化钼(MoS2)

2.2.2. 跟着传统晶体经管造本事瓶颈的镇定泄露,为擢升芯片缱绻智力、减轻芯片尺寸,新式堆叠本事也成为该规模的主要本事研发主张

2.3. 基于单层黑磷和砷化锗的新式晶体管

2.3.1. 一种范德华剥离本事(van der Waals exfoliation),胜利使用这种本事创建了基于黑磷和砷化锗的晶体管,并解释了其优厚的电学本性

2.3.2. 在斥地基于其他不默契单层材料的晶体管方面的后劲,这种本事八成减薄晶体管的沟说念部分,同期保抓斗争区域所需的厚度

2.3.3. 为使用二维半导体材料制造更薄、更可膨大的电子成立开辟了新的阶梯

2.4. 新式氮化铝功率半导体,可大幅假造电力损耗

2.4.1. 标明氮化铝半导体品性素雅,但愿五年后发布多种基于氮化铝的元器件

2.5. 众人首款可应用于集成电路的N型场效应晶体管

2.5.1. 天下上首款可应用于集成电路(CMOS)的N型场效应晶体管(MOSFET)

2.5.2. 使用NIMS专有的微波等离子体化学气相千里积(MPCVD)智力精确限制高温高压合成(HPHT)单晶金刚石基板晶面上的掺杂浓度,最终形成了高品性的N型金刚石外延层,并基于此研发出新式N型场效应晶体管

2.5.3. 该N型金刚石MOSFET在300摄氏度下场效应电子移动率约为150平方厘米/伏特·秒(cm²/V·sec)

2.5.4. 该盘考可应用于集成电路的斥地,如用于制造恶劣环境中使用的电子器件和传感器等

2.6. 在晶圆上集成了二硫化钼晶体管,可减轻芯片尺寸

2.6.1. 胜利在一个200毫米的晶圆上集成了二硫化钼(MoS2)晶体管,可减轻芯片尺寸

2.6.2. 使用金属有机化学气相千里积(MOCVD)本事制造出大限制MoS2场效应晶体管(FET),比肩除了MoS2材料与金属界面之间的肖特基势垒,从而大大增强了FET的载流子移动率

2.6.3. MoS2FET在场效应移动率、斗争电阻和电流密度等方面均优于其他MoS2 FET

2.7. 斥地出新式铁电晶体管

2.7.1. 在正负电荷之间以极高的速率切换来模拟缱绻机编码中的“0”和“1”,经过1000亿次开关后仍保抓平素使命,厚度仅为十亿分之一米

2.7.2. 性能优厚,将来有望用于逻辑运算成立和非易失性存储成立

2.8. 斥地出新式二维低功耗场效应晶体管

2.8.1. 2024年8月,中国科学院上海微系统与信息本事盘考所、香港城市大学和复旦大学融合盘考团队斥地出新式二维低功耗场效应晶体管

2.8.2. 使用厚度仅为1.25纳米的单晶氧化铝,遴荐轨范范德华转动智力制造了具有高品性介电界面的二维场效应晶体管

2.8.3. 栅极宽度为100微米,长度为250纳米,通过在栅极之间留有裂缝,确保了皆备的绝缘性

2.8.4. 处分了高栅极走电和低介电强度问题,有望推动下一代微型化电子成立的发展

2.9. 斥地出基于二维半导体制造高性能晶体管的智力

{jz:field.toptypename/}2.9.1. 2024年9月,中国苏州大学、沙特阿拉伯阿卜杜拉国王科技大学和奥地利维也纳工业大学等机构的盘考东说念主员斥地出一种基于二维半导体制造高性能晶体管的智力

2.9.2. 依赖于六方氮化硼(h-BN)电介质和具有高内聚能的金属栅极电极

2.9.3. h-BN栅极电介质与铂和钨等高内聚能金属的兼容性最好,不错有用减少走电流

2.9.4. 与遴荐金电极的雷同晶体管比拟,基于铂和钨的栅极电极可将h-BN介电体上的走电流假造至底本的约1/500,这故意于把握二维材料制造可靠的固态微电子电路和成立

2.10. 研发出新式电子堆叠本事,可显赫增多芯片上的晶体管数目

2.10.1. 胜利制造出多层芯片,其中高品性半导体不再局限于传统的硅基底,而是轮换滋长顺利叠加在沿途,从而改善层间通讯质地与速率

2.10.2. 使芯片八成卓越传统收尾进行堆叠,大幅擢升了东说念主工智能、逻辑运算及内存应用的缱绻智力

3. 先进制造工艺

3.1. 跟着摩尔定律的放缓,新的先进制造工艺崭露头角,如3D集成本事、异构集成本事等,不再单纯依赖晶体管数目的增长来擢升性能

3.2. 加之行业对先进芯片的需求量不停增多,制酿老本不停升高,先进封装本事、极紫外光刻替代本事等新工艺应时而生,有望在新的芯片制造本事迭代、老本效益擢升上阐明积极作用

3.3. 展示大限制半导体3D集成

3.3.1. 单片3D集成提供了更高密度的垂直勾通,因为不依赖于两个事先图案化芯片的黏合,这种集成智力不错增多芯片上的晶体管数目,进一步延续摩尔定律

3.3.2. 有助于提高缱绻智力和假造功耗,并为电子成立添加新的功能,如在缱绻芯片中整合传感器等,将成立垂直堆叠在沿途,不错裁减成立之间的距离,从而减少延长和功耗

3.4. 瑞萨电子公司研发出新本事,可使AI芯片性能提高16倍

3.4.1. 斥地出可使东说念主工智能半导体的处感性能最多提高16倍的本事

3.4.2. 不仅显赫擢升了性能,同期还将每瓦电力的运算智力推至每秒10万亿次浮点运算,而耗电量却能限制在原有水平的八分之一以下

3.4.3. 这项本事的紧闭意味着东说念主工智能本事将迎来更大发展空间

3.5. Cerebras公司推出晶圆级新式AI处理器WSE-3

3.5.1. WSE-3的单芯片尺寸达到46225平方毫米,比英伟达H100处理器大57倍

3.5.2. 单块WSE-3芯片领有4万亿个晶体管和90万个AI中枢,峰值性能达到每秒125千万亿次浮点运算,通过中国台积电5纳米工艺进行制造

3.5.3. 将用于推行一些业界最大的东说念主工智能模子,米兰体彩下载如能推行多达24万亿个参数的AI模子

3.5.4. 通过WSE-3加强应答与英伟达公司的竞争

3.6. 新的EUV光刻机替代决策

3.6.1. 筑波高能加快器盘考组织(KEK)盘考东说念主员淡薄一种新的EUV光刻机替代决策

3.6.2. 触及把握粒子加快器的能量来兑现更经济、更快速、更高效的EUV光刻本事

3.6.3. EUV光刻的最好替代候选决策是斥地能量回收线性加快器,使用粒子加快器版块的再生制动

3.6.4. 解放光子激光(FEL)光束的高功率、窄谱宽使FEL相等合乎用于将来的光刻本事

3.6.5. 不错用相对更低的老本产生数十千瓦的坚硬解放电子激光,以驱动多台下一代光刻机,从而假造先进芯片制造的老本

3.7. 佳能公司初次拜托纳米压印光刻成立

3.7.1. 旨趣是像钤记不异将印有电路图案的掩模版压入晶圆上的光刻胶中,同期,耗电量仅为EUV光刻机的十分之一

3.7.2. NIL光刻成立在假造功耗和老本的情况下,八成兑现最小线宽14纳米的图案化,尽头于5纳米制程本事

3.7.3. 经过进一步纠正,瞻望还能分娩2纳米产物

3.7.4. 其纳米压印光刻机的计谋不是取代晶圆厂的DUV和EUV器具,而是与现存器具共存

3.8. 华科武汉光电国度盘登科心攻克芯片光刻胶纰谬本事

3.8.1. 研发出T150A光刻胶系列产物,已通过半导体工艺量产考据,兑现了原材料全部国产,配方全自主联想

3.8.2. T150A在光刻工艺中阐发出的极限诀别率达到120纳米,且工艺宽宏度更大、默契性更高、留膜率更优,对刻蚀工艺阐发更好

3.8.3. T150A中的密集图形经过刻蚀,基层介质的侧壁垂直度阐发优

3.8.4. 将来还会发展一系列应用于不同场景下的KrF与ArF光刻胶,努力于紧闭国际“卡脖子”纰谬本事

3.9. 机械材料盘考所研发出众人首个4英寸异构结构半导体

3.9.1. 初次胜利把握等离子体增强化学气相千里积(PECVD)本事制造出4英寸异质结构半导体

3.9.2. 可兑现WS2/石墨烯和1T-2H MoS2异质结构的大面积制备,为兑现3D集成结构、假造功耗和擢升性能能效奠定基础

3.10. 博通推出业界首个3.5D F2F封装本事

3.10.1. 推出业界首个3.5D F2F封装本事和3.5D XDSiP封装平台本事

3.10.2. 该本事使用创新的F2F堆叠表情顺利勾通顶层金属层,在单一封装中集成朝上6000平方毫米的硅芯片和多达12个HBM内存堆栈,既兑现了密集可靠的勾通,又可最小化电气打扰,具有极佳的机械强度,同期在封装尺寸上也具备上风

3.10.3. 3.5D XDSiP平台专为高性能AI和HPC处理器联想,可得志AI芯片高收尾、低功耗的缱绻需求

3.11. 香港科大斥地众人首款高光效深紫外骄横晶圆,推动无掩模光刻本事发展

3.11.1. 众人首个用于光刻机的深紫外micro-LED骄横阵列晶圆

3.11.2. 兑现多项纰谬性本事紧闭,如相助无掩模紫外光光刻本事,可有用擢升其光输出功率密度准确性、图案骄横理解度、荧幕性能、快速曝光智力等,兑现了以较低老本和更高效的智力推动半导体晶片分娩的本事发展

4. 新式存储本事

4.1. 新式存储本事是指在硬盘(HDD)、固态硬盘(SSD)等传统存储本事以外,通过创新的材料、架构、缱绻旨趣或操作表情兑现的数据存储,主要包括相变存储、磁变存储、阻变存储、铁电存储、存算一体化等

4.2. 具有擢升存储速率、提高存储密度、增强数据耐用性、假造功耗等上风,八成弥补传统存储本事在高性能缱绻、大数据处理等规模的不及

4.3. 新式存储本事的发展也为量子缱绻、超算、东说念主工智能等新兴本事规模提供了有劲因循

4.4. 清华大学斥地出液态电阻式赶紧存取存储器

4.4.1. 2024年1月,中国清华大学刘静团队斥地出液态电阻式柔性赶紧存取存储器(FlexRAM),可用于柔性电路

4.4.2. 使用镓基液态金属兑现FlexRAM的数据写入和读取历程,镓基液态金属液滴通过氧化和收复机制模拟对神经元超极化和去极化的溶液环境变化历程进行仿真

4.4.3. FlexRAM还具有可重叠使用性,可在朝上3500次操作轮回中保抓默契的性能

4.4.4. 从压根上编削了传统的柔性存储见地,为将来软智能机器东说念主、脑机接口系统、可一稔/植入电子成立提供了表面基础和本事旅途

4.5. 台积电斥地出SOT-MRAM阵列芯片,功耗仅为雷同本事的1%

4.5.1. 研发出自旋轨说念力矩式磁性内存(SOT-MRAM),功耗仅为雷同本事STT-MRAM的百分之一

4.5.2. SOT-MRAM是下一代磁阻式赶紧存取内存(MRAM)本事,可得志新一代内存需求,现在三星、英特尔等大厂都在加大干与研发该本事

4.5.3. 跟着AI、5G期间的驾临,自动驾驶、精确医疗会诊、卫星影像辨识等场景应用,都需要更快、更稳、功耗更低的新一代内存

4.6. 华为公司将推出新式磁电存储成立

4.6.1. 该成立基于磁电磁盘(MED)本事

4.6.2. 不错假造总勾通老本和功耗,第一代产物定位为大容量档案存储,机架容量朝上10拍字节,功耗小于2千瓦

4.6.3. MED本事不错提供比传统硬盘和磁带存储更低的老本和功耗

4.7. 基于斯格明子的低功耗存储本事

4.7.1. 斥地出基于斯格明子(Skyrmion)的低功耗存储本事

4.7.2. 斯格明子是一种轻细快速的磁涡流,不错行为高效的东说念主工智能缱绻的理思载体

4.7.3. 胜利兑现了斯格明子的电读出和景象之间的电切换,解释了其在高效、可抓续东说念主工智能缱绻中的广泛后劲

4.7.4. 功耗比现存生意存储本事的功耗低1000倍,为将来更快、更节能的缱绻本事铺平了说念路

365建站客服QQ:8000836524.8. 铠侠公司将引入低温蚀刻本事,可加快存储芯片制造

4.8.1. 将从其第10代NAND产物运行,在制程中引入低温蚀刻法这一前沿本事,进一步擢升分娩收尾

4.8.2. 比拟传统的电浆蚀刻法,低温蚀刻法的加工速率擢升了约4倍,艳丽着存储本事的一次热切立异

4.8.3. 这项创新本事可在短短33分钟内兑现10微米深的高纵横比(晶圆上形成的图案的深度与宽度之比)蚀刻

4.8.4. 除铠侠公司外,三星电子公司也计算遴荐低温蚀刻本事制造芯片

4.9. 深圳大学研发出一款新式感存算一体化的无浮栅型光电闪存器

4.9.1. 遴荐旋涂法将红外光感知材料上的退换纳米颗粒与有机半导体聚(3-己基噻吩)均匀夹杂,从而形成具有默契光反馈本性的复合材料体系,再将其与多级电导态光电晶体管结合,兑现了感知、存储和处理等功能的和会

4.9.2. 不仅能显赫擢升数据处理收尾,况且其具备的多级存储和高维非线性抒发智力使得复杂时序数据的高效处理成为可能

4.9.3. 弥补了传统材料在红外感知方面的不及,兑现了在窄带近红外放射下信息的有用赢得和处理,为红外机器视觉的应用带来可能